Bài 11: Sự chậm trễ truyền dữ liệu trong FPGA

Làm thế nào để khắc phục sự chậm trễ tuyên dữ liệu với Pipelining

Độ trễ truyền là khoảng thời gian để tín hiệu di chuyển từ nguồn đến đích. Sự chậm trễ truyền là một khái niệm cơ bản về cách thức các mạch kỹ thuật số hoạt động. Rõ ràng tất cả các tín hiệu không thể truyền đi ngay lập tức. Phải mất một khoảng thời gian rất nhỏ để thay đổi điện áp lan truyền xuống dây. Quy tắc chung là các tín hiệu có thể di chuyển đến một PIN trong một nano giây .

Bên trong FPGA hoặc ASIC có hàng ngàn dây nhỏ chạy khắp nơi. Khi bạn thêm chiều dài vật lý của dây, chiều dài của dây nối càng lớn. Ngoài ra, mỗi đoạn logic mà mã của bạn trải qua sẽ mất một số thời gian trễ hữu hạn. Vì những sự chậm trễ này tồn tại, nhà thiết kế kỹ thuật số cần phải hiểu cách chúng tác động đến FPGA hoặc ASIC.

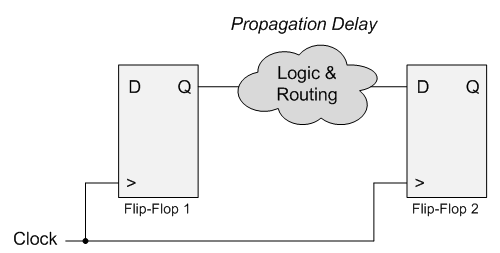

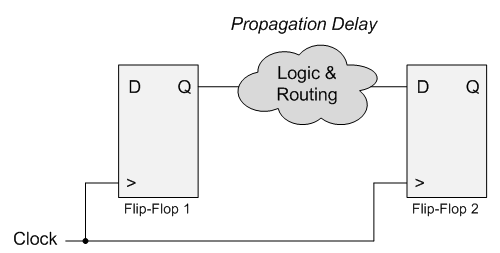

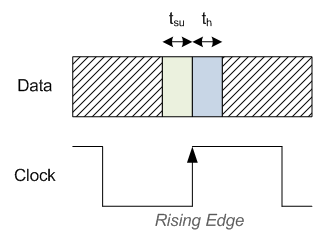

Sự chậm trễ truyền là vấn đề cơ bản quan trọng trong logic tuần tự . Logic tuần tự là logic được điều khiển bởi một đồng hồ. Trong hình trên, có hai Flip-Flops được kết nối cùng với một số logic và định tuyến (dây) giữa chúng. Lượng thời gian cần thiết cho đầu ra của Flip-Flop trước để di chuyển đến đầu vào của Flip-Flop thứ hai là Sự chậm trễ truyền. Độ trễ truyền càng lớn, đồng hồ của bạn phải càng chạy chậm.

Lý do cho điều này là cả Flip-Flops đều sử dụng cùng một đồng hồ. Flip-Flop đầu tiên đẩy dữ liệu đầu ra của nó ở cạnh đồng hồ 1. Flip-Flop thứ hai không thấy sự thay đổi trên đầu ra của Flip-Flop đầu tiên cho đến cạnh đồng hồ 2, tại thời điểm đó nó đẩy đầu ra của nó. Nếu tín hiệu có thể di chuyển an toàn từ Flip-Flop 1 sang Flip-Flop 2 trong một khoảng thời gian đồng hồ, thiết kế của bạn là tốt! Nếu không, bạn sẽ gặp vấn đề.

Ví dụ, hãy xem xét trường hợp bạn có hai Flip-Flops cách nhau 10 nano giây (ns). Nếu bạn sử dụng đồng hồ chạy ở tốc độ 50 MHz (khoảng thời gian 20 ns), dữu liệu sẽ được an toàn. Bạn có 10 ns để phụ tùng. Tuy nhiên nếu bạn sử dụng đồng hồ 200 MHz (khoảng thời gian 5 ns), thiết kế của bạn sẽ không phân tích thời gian và không hoạt động theo cách bạn mong đợi.

Mục đích của bất kỳ bộ phân tích thời gian nào trong FPGA hoặc ASIC là để cho bạn biết nếu bạn gặp vấn đề về thời gian. Nếu thiết kế của bạn quá chậm để chạy ở tần số đồng hồ bạn muốn, bạn sẽ nhận được lỗi thời gian và thiết kế của bạn có thể sẽ không hoạt động chính xác.

Đây là cách bạn có thể khắc phục sự chậm trễ truyền:

- Làm chậm tần số đồng hồ của bạn;

- Tách logic của bạn thành các giai đoạn (đường ống).

Làm chậm tần số đồng hồ của bạn là điều hiển nhiên nhất. Nếu bạn có thể chạy FPGA của bạn chậm hơn, thời gian của bạn sẽ cải thiện. Tách logic của bạn thành các giai đoạn là giải pháp mạnh mẽ hơn. Nếu bạn làm ít "thứ" giữa hai Flip-Flops, độ trễ truyền sẽ giảm và thiết kế của bạn sẽ đáp ứng thời gian.

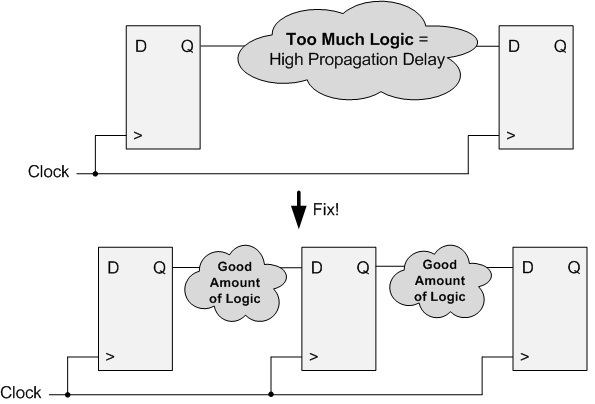

Trong hình trên, có một số lượng lớn logic giữa hai Flip-Flops. Vì vậy, sinh ra chậm trễ nhiều, Nếu nhà thiết kế tách logic thành ba Flip-Flops, một nửa logic có thể được thực hiện giữa hai Flip-Flops đầu tiên và nửa còn lại của logic có thể được thực hiện giữa hai thứ hai. Bây giờ các công cụ sẽ có gần gấp đôi thời gian để làm những gì bạn cần trong một chu kỳ đồng hồ duy nhất . Điều này được gọi là pipelining và điều này rất quan trọng để trở thành một nhà thiết kế kỹ thuật số tốt. Khi bạn thiết kế mã của bạn trong một pipeline, làm tăng khả ăng đáp ứng thời gian ở tần số xung nhịp cao.

Đừng cố gắng làm quá nhiều trong một chu kỳ đồng hồ! Sự chậm trễ sẽ quá dài. Thay vào đó, hãy thiết kế theo pipeline!

Bình luận gần đây