Bài 8: FIPO là gì?

Bộ đệm FIFO được sử dụng để truyền dữ liệu.

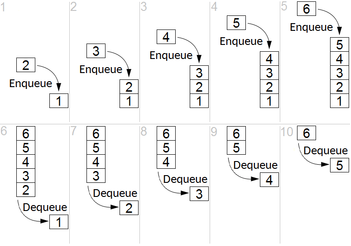

Từ FIFO là viết tắt của First In First Out. FIFO được sử dụng ở mọi nơi trong thiết kế FPGA và ASIC, chúng là một trong những khối xây dựng cơ bản. Và chúng rất tiện dụng! FIFO có thể được sử dụng cho bất kỳ mục đích nào sau đây:

- Chuyển đổi dữ liệu trong các miền Clocks;

- Dữ liệu đệm trước khi gửi nó ra khỏi chip (ví dụ DRAM hoặc SRAM);

- Buffering dữ liệu cho phần mềm để xem xét tại một số thời gian sau đó;

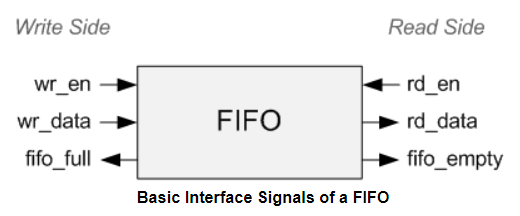

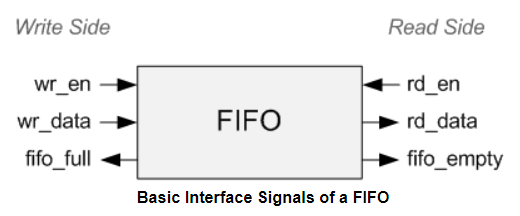

- Lưu trữ dữ liệu để xử lý sau. Một FIFO có thể được nghĩ đến một đường hầm một chiều mà xe ô tô có thể đi qua. Ở cuối đường hầm là một trạm thu phí. Khi cánh cổng mở ra, chiếc xe có thể rời khỏi đường hầm. Nếu cánh cổng đó không mở ra và nhiều ô tô tiếp tục đi vào đường hầm, cuối cùng đường hầm sẽ đầy xe. Điều này được gọi là tràn FIFO và nói chung đây không phải là một điều tốt. Làm thế nào FIFO sâu có thể được coi là chiều dài của đường hầm. FIFOSâu hơn, càng có nhiều dữ liệu có thể phù hợp với nó trước khi nó tràn. FIFO cũng có chiều rộng, đại diện cho chiều rộng của dữ liệu (về số bit) đi vào FIFO. Dưới đây là hình ảnh về giao diện cơ bản của bất kỳ FIFO nào. Những tín hiệu này sẽ luôn luôn được tìm thấy khi bạn nhìn vào bất kỳ FIFO. Thường thì có nhiều tín hiệu thêm các tính năng bổ sung, chẳng hạn như số lượng từ trong FIFO. Xem hình bên dưới:

FIFO có thể được chia thành nửa ghi và nửa đọc. Nửa ghi bao gồm: Write Enable, Write Data, và FIFO Full. Nhà thiết kế không bao giờ nên ghi dữ liệu để cho FIFO tràn! Do đó luôn kiểm tra cờ toàn FIFO để đảm bảo có chỗ trống cho khung dữ liệu khác, nếu không bạn sẽ mất dữ liệu đó.

Một nửa đọc bao gồm: Read Enable, Read data và FIFO Empty. Tôi thấy dễ dàng hơn khi thiết kế mã riêng cho phần đọc và phần ghi dữ liệu ở các tệp khác nhau, chỉ cần cẩn thận. Nhà thiết kế không bao giờ nên đọc từ một FIFO trống! Miễn là bạn tuân thủ hai quy tắc cơ bản này, FIFO sẽ trở nên độc đáo. Có thể nhắc lại hai qui tắc cực ký quan trọng của FIFO là:

- Không bao giờ ghi vào một FIFO đầy (overflow);

- Không bao giờ đọc từ một FIFO trống (underflow).

Bản thân FIFO có thể được tạo thành từ các phần logic chuyên dụng bên trong FPGA hoặc ASIC hoặc chúng có thể được tạo ra từ Flip-Flops (các thanh ghi phân phối). Mà một trong hai công cụ tổng hợp sẽ sử dụng là hoàn toàn phụ thuộc vào nhà cung cấp FPGA mà bạn đang sử dụng và cách bạn cấu trúc mã. Chỉ cần biết rằng khi bạn sử dụng các mẩu logic chuyên dụng, chúng có hiệu suất tốt hơn so với FIFO dựa trên đăng ký.

FIFO là một trong những khối xây dựng cơ bản cho các nhà thiết kế FPGA và rất quan trọng để hiểu và sử dụng chính xác!

1 Response

[…] Bài 8: FIPO là gì? – izTuts […]