Bài 4: LUT – Look up Table – Bảng tra trong FPGA

Nhanh quá, mới đó mà đã sang bài 4!

Trong các bài trước, chúng ta đã thảo luận về các vấn đề cơ bản của Đại số Boolean, cụ thể là các cổng AND, OR, NOT, XOR và NAND hoạt động như thế nào. Khái niệm về các bảng chân lý đã được thảo luận. Trong bài này, chúng ta sẽ mở rộng về chủ đề này về cách các bảng chân lý hoạt động khi có sự phối hợp các cổng theo các sơ đồ phức tạp hơn.

Vì sao phải là bảng tra?

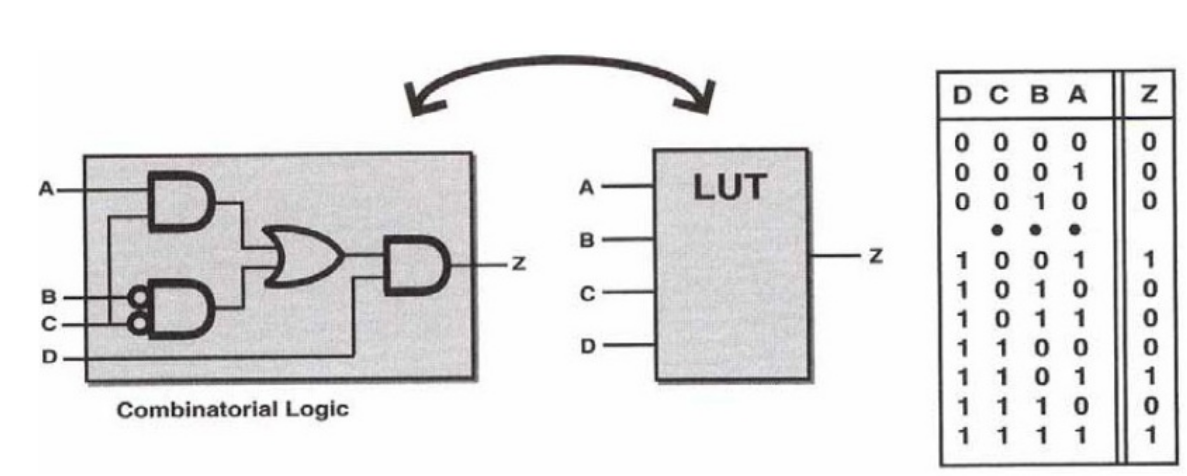

Đầu tiên cần lưu ý rằng tất cả các cổng logic rời rạc mà chúng ta đã thảo luận trước đây (AND, OR, vv) thực sự không tồn tại bên trong một FPGA! Tuy nhiên, có thể thực hiện các chức năng đó. Cách mà FPGA có thể làm là sử dụng bảng tra cứu (LUT) như kiểu bảng chân lý. Bảng tra cứu là một khối chức năng rời rạc có thể được lập trình bởi Nhà thiết kế kỹ thuật số. LUT sử dụng cùng một khái niệm bảng chân lý để liên kết kết quả đầu ra với đầu vào. Hãy thử một ví dụ.

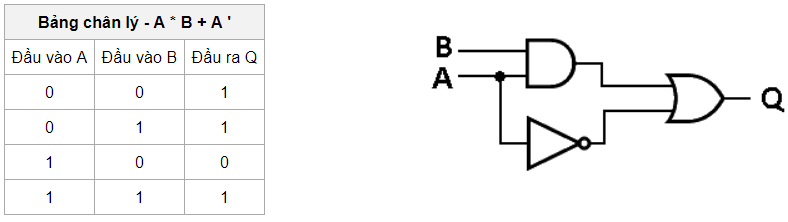

Tạo một bảng chân lý cho phương trình Boolean sau đây: Q = A * B + A'. Có lẽ chúng ta nên xác định ý nghĩa của những biểu tượng đó.

* = AND

+ = OR

' = NOT

^ = XOR

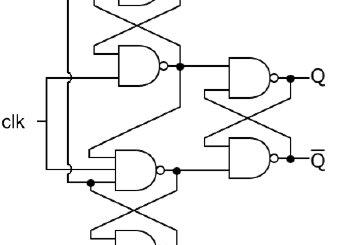

Vì vậy, bằng lời nói, phương trình Boolean Q = A * B + A 'có thể được đọc, "Đầu ra Q nhận A và B hoặc không A". Hãy nhìn vào bảng chân lý và mạch được tạo ra bởi phương trình này. Như nó có thể được nhìn thấy từ hình ảnh dưới đây, phải mất ba tổng số cổng để làm cho mạch này.

Bảng chân lý trong ví dụ trên có hai đầu vào (A và B), có nghĩa là có bốn khả năng xẩy ra. Khi số lượng đầu vào tăng lên 1 thì số lượng đầu ra tăng lên mũ 2 lần. Vì vậy, với một đầu vào có 2 khả năng đầu ra, cho 2 đầu vào có 4 khả năng đầu ra, cho 3 đầu vào 8 khả năng đầu ra, vv...

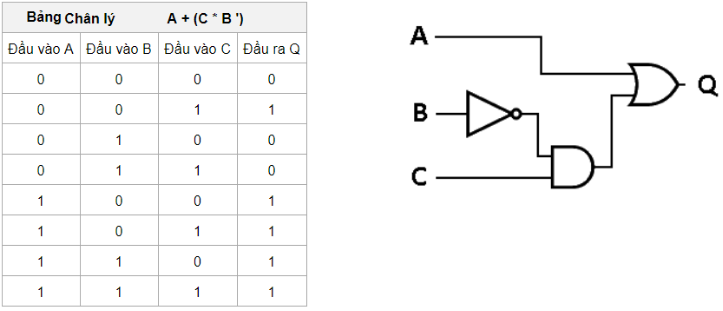

Bây giờ chúng ta hãy xem xét một ví dụ nữa với ba đầu vào. Đây là phương trình chúng ta sẽ tạo một bảng chân lý cho: Q = A + (C * B '). Lưu ý rằng dấu ngoặc đơn chỉ ra rằng toán tử C VÀ NOT B xẩy ra trước toán tử OR.

Như đã đề cập ở phần đầu của bài viết này, các cổng logic rời rạc không thực sự tồn tại bên trong một FPGA. Thay vào đó, các FPGA sử dụng các bảng tra cứu hoặc các LUT. LUT được lập trình bởi Digital Designer để thực hiện một phương trình đại số Boolean giống như hai phương trình mà chúng ta đã thấy ở trên.

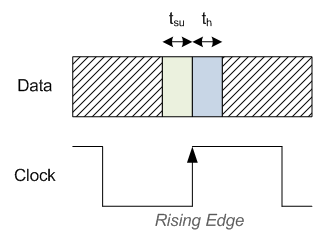

Với 3 tín hiệu đầu vào LUT có thể đại diện cho bất kỳ phương trình Boolean nào, rất nhanh gọn mà không cần sơ đồ phức tạp. LUT có thể có kích thước khác nhau tùy thuộc vào FPGA mà bạn đang sử dụng, nhưng tất cả đều hoạt động theo cùng một cách. Nếu bạn cần thực hiện một biểu thức phức tạp hơn, bạn chỉ có thể sử dụng nhiều Bảng tra cứu hơn. LUT là một trong hai thành phần cơ bản nhất trong một FPGA. Một FPGA duy nhất có hàng ngàn thành phần này. Một thành phần khác cũng vô cùng quan trọng trong FPGA là Flip-Plop sẽ được thảo luận trong bài tiếp theo.

Bình luận gần đây