Bài 9: Chốt là gì? (Latch)

Latch trong FPGA là gì?

Khuyến cáo: Bạn không nên sử dụng chốt trong thiết kế FPGA! Nếu bạn không biết những gì bạn đang làm bạn có thể vô tình được tạo ra chốt với mã HDL và điều này có lẽ là một điều rất xấu . Đầu tiên hãy thảo luận về một chốt là gì, sau đó bài viết tiếp theo để xem chúng được tạo ra như thế nào trong mã HDL và tìm hiểu cách tránh tạo ra chúng một cách vô tình!

Các chốt thông thường được tạo ra bởi các công cụ tổng hợp (các công cụ chuyển đổi mã Verilog hoặc VHDL của bạn thành các thành phần FPGA cấp thấp) là Gated D Latch. Tuy nhiên có các loại chốt khác: SR Latch, D Latch, JK Latch và Earle Latch . Các chức năng cá nhân của những điều này không được thảo luận chi tiết ở đây.

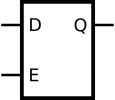

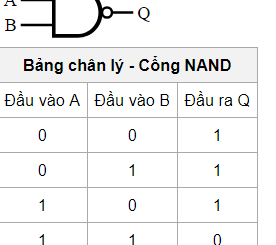

Chốt D Gated có hai đầu vào và một đầu ra. Sơ đồ khối được hiển thị bên dưới. Đầu vào D là đầu vào Dữ liệu của bạn. Điều này chứa giá trị mà bạn muốn đầu ra để đi đến. Input E là đầu vào Enable của bạn. Đầu ra Q chỉ nhận giá trị trên D khi Enable là 1. Khi Enable là 0, nó không quan trọng những gì đầu vào D đang làm, đầu ra sẽ không thay đổi. Nó giữ giá trị trước đó của nó, do đó tại sao nó được gọi là chốt! Đầu ra được chốt khi bật thấp .

| Bảng Chân lý - Gated D Latch | ||

|---|---|---|

| Đầu vào D | Đầu vào E | Đầu ra Q |

| X | 0 | Q Trước |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

Bây giờ, tôi đề nghị rằng chốt không bao giờ nên được sử dụng bởi vì chúng rất nguy hiểm. Có hai lý do chính cho việc này:

- Thường thì người dùng đã tạo ra chốt đã vô ý. Rất có khả năng mã HDL được viết không thực sự là ý tưởng của nhà thiết kế.

- Chúng có thể gây khó khăn cho các công cụ FPGA . Thông thường, chúng tạo thêm sự chậm trễ định tuyến đáng kể và có thể khiến thiết kế của bạn không đáp ứng được thời gian.

Hãy tiếp tục thảo luận về chốt với một cuộc thảo luận về cách có chốt được tạo ra trong VHDL và Verilog? Chúng ta sẽ học cách viết mã để tránh việc tạo ra các chốt hoàn toàn trong các bài sau.

Bình luận gần đây