Bài 15: Ngôn ngữ mô tả phần cứng nào cho bạn? VHDL hay Verilog

VHDL hay Verilog

Bạn nên sử dụng ngôn ngữ nào cho thiết kế FPGA và ASIC của mình?

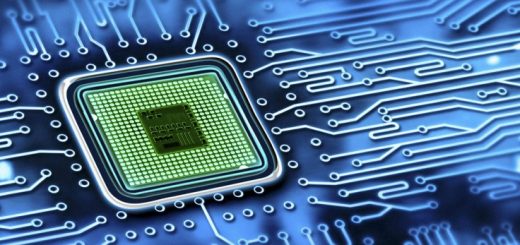

Câu hỏi liệu Verilog hay VHDL tốt hơn cho người mới bắt đầu có được hỏi mọi lúc không. Cả hai ngôn ngữ đều có thể được sử dụng để tạo mã chạy trên FPGA và ASIC . Nói chung có một số điểm mà bạn nên biết.

- VHDL được gõ mạnh mẽ. Điều này làm cho nó khó khăn hơn để làm cho những sai lầm như một người mới bắt đầu bởi vì trình biên dịch sẽ không cho phép bạn viết mã đó là hợp lệ. Verilog bị đánh máy yếu. Nó cho phép bạn viết mã sai, nhưng ngắn gọn hơn.

- Verilog trông gần gũi hơn với một ngôn ngữ phần mềm như C. Điều này làm cho nó dễ dàng hơn cho một người biết C cũng đọc và hiểu những gì Verilog đang làm.

- VHDL đòi hỏi rất nhiều đánh máy. Verilog thường yêu cầu ít mã hơn để làm điều tương tự.

- VHDL là rất xác định, nơi Verilog là không xác định trong những trường hợp nhất định.

Ảnh này hiển thị bảng phân tích rõ ràng hơn theo quốc gia theo quốc gia VHDL so với Verilog. Châu Âu, Nam mỹ, Úc sử dụng VHDL nhiều hơn, Còn lại Châu Á, Bắc Mỹ sử dụng Verilog nhiều hơn. Thông tin khác rằng ngành công nghiệp quốc phòng Hoa Kỳ nói chung ủng hộ VHDL, trong khi ngành công nghiệp thương mại ủng hộ Verilog. Lưu ý rằng ở Đức và Pháp, VHDL phổ biến hơn Verilog. Nếu bạn đến từ một trong hai quốc gia này, tôi rất khuyên bạn nên học VHDL trước tiên! Ở Trung Quốc và Hàn Quốc, chúng ta có thể thấy rằng Verilog phổ biến hơn nhiều so với VHDL, vì vậy hãy điều chỉnh các ưu tiên của bạn cho phù hợp.

Nói chung, VHDL và Verilog là những ngôn ngữ có khả năng tương đương nhau. Bạn nên căn cứ quyết định của bạn về ngôn ngữ để tìm hiểu dựa trên những gì phổ biến nhất cho vị trí và hoàn cảnh của bạn. Hãy bắt đầu học!

Ở Việt Nam, Verilog phổ biến hơn, nhưng tốt nhất là học cả 2!

Bình luận gần đây