Bài 13: Metastability trong FPGA là gì?

Metastability trong FPGA là gì?

Nếu bạn đã từng thử dùng một số đầu vào cho FPGA, chẳng hạn như một nút bấm, hoặc nếu bạn đã phải qua các lĩnh vực đồng hồ, bạn đã phải đối phó với Metastability. Một trạng thái metastable là trạng thái đầu ra của Flip-Flop bên trong FPGA không biết hoặc không xác định. Khi tình trạng này xảy ra, không có cách nào để biết liệu đầu ra của Flip-Flop của bạn sẽ là 1 hay 0. Điều kiện xảy ra Metastability khi thời gian thiết lập hoặc thời gian giữ bị vi phạm.

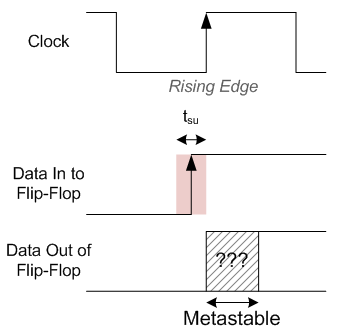

Metastability là điều xấu: Nó có thể làm cho FPGA có hành vi rất lạ. Hình bên trên minh họa về metastable. Vùng màu đỏ đại diện cho t su hoặc Time Setup. Như bạn có thể thấy, đầu vào dữ liệu cho Flip-Flop đã đi từ thấp đến cao trong suốt thời gian thiết lập của Flip-Flop. Điều này làm cho đầu ra bị metastable. tức là không biết là 0 hay 1. Một lần nữa, đây không phải là hành vi mong muốn. Bạn phải luôn luôn biết những gì FPGA của bạn đang làm.

Metastability là điều xấu: Nó có thể làm cho FPGA có hành vi rất lạ. Hình bên trên minh họa về metastable. Vùng màu đỏ đại diện cho t su hoặc Time Setup. Như bạn có thể thấy, đầu vào dữ liệu cho Flip-Flop đã đi từ thấp đến cao trong suốt thời gian thiết lập của Flip-Flop. Điều này làm cho đầu ra bị metastable. tức là không biết là 0 hay 1. Một lần nữa, đây không phải là hành vi mong muốn. Bạn phải luôn luôn biết những gì FPGA của bạn đang làm.

Làm thế nào để ngăn chặn Metastability

Hầu hết các điều kiện siêu bền xảy ra theo một trong hai cách:

- Bạn đang lấy mẫu tín hiệu bên ngoài vào FPGA;

- Bạn đang chuyển các miền đồng hồ

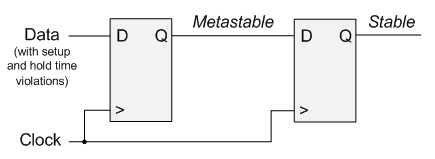

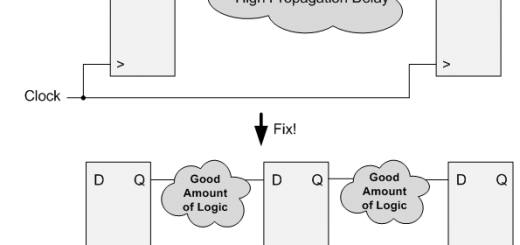

Cả hai tình huống này có thể được sửa theo cùng một cách. Bất cứ khi nào bạn gặp phải một tình huống có thể tạo ra Metastability, bạn có thể chỉ cần "double-flop" dữ liệu của bạn.

Trong hình trên, một tín hiệu không đồng bộ với đồng hồ đang được lấy mẫu bởi Flip-Flop đầu tiên. Điều này sẽ tạo ra một Metastability ở đầu ra. Nếu bạn lại lấy mẫu đầu ra này, bây giờ bạn có thể sửa sự kiện có thể thay đổi của mình. Đầu ra của Flip-Flop thứ hai sẽ ổn định .

Để đọc thêm về Metastability, bao gồm cả khoa học đằng sau nó (và rất nhiều thông tin kỹ thuật về tỷ lệ thất bại và như vậy) Altera đã viết một bài báo rất chi tiết về nó.

Bình luận gần đây