Bài 5: Flip-Flop – Thành phần quan trọng nhất trong FPGA?

Chán nhỉ? Đọc tới bài này thì chúng ta mới biết các bài trước chúng ta bị lừa! Tìm hiểu về các cổng logic làm gì! Học luôn về LUT cho rồi đi! Vì thành phần cơ bản trong FPGA là các LUT chứ có cái cổng Logic nào đâu? Tuy nhiên, chúng ta nên nhớ rằng: "Bên trong LUT chứa các cổng logic".

Flip-Flop - Thành phần quan trọng nhất trong FPGA?

Từ từ nhé! Đừng gật mình, đến đây chúng ta cần biết là trong FPGA có LUT và một thành phần khác là Flip-Flop (chưa biết nó là gì). Đọc dần xuống dưới để hiểu Flip-Flop nhé!

Trong phần trước, chúng tôi đã thảo luận về thành phần bảng tra cứu (LUT). Đây là một trong hai thành phần quan trọng nhất bên trong một FPGA, thành phần quan trọng nhất khác là Flip-Flop. Có một vài loại flip-flops khác nhau (JK, T, D) nhưng một trong đó được sử dụng thường xuyên nhất là D Flip-Flop .

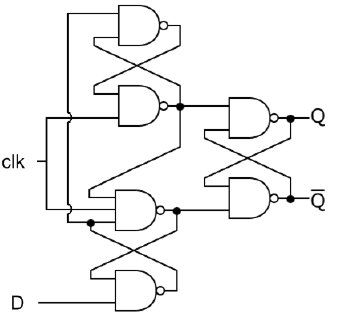

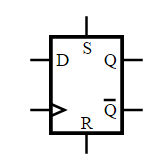

Hình bên mô tả một Flip-Flop

Trong Flip-Flop có một chân S ở phía trên cùng được gọi là Set pin (chân cài đặt). Ở dưới cùng của khối có một pin R được gọi là Reset pin (Chân đặt lại). Ngoài ra, ở bên phải của thiết bị, có một pin có nhãn Q gạch. Pin này sẽ luôn luôn chứa giá trị ngược lại của giá trị trên pin Q. Những Pin này không quan trọng lắm và không cần quan tâm. Chúng ta chỉ cần quan tâm đến 3 chân (PIN) cơ bản trong Flip-Flop là:

- Đầu vào dữ liệu D cho Flip-Flop;

- Đầu ra dữ liệu Q của Flip-Flop;

- Đầu vào đồng hồ > cho Flip-Flop.

Câu hỏi đầu tiên bạn có thể tự hỏi là đồng hồ là gì? Nếu các bạn biết chút ít về vi xử lý thì có lẽ cũng sẽ biết tốc độ hoạt động của CPU được thể hiện qua mạch dao động (thường làm bằng thạch anh). Đây chính là đồng hồ kỹ thuật số.

Trong FPGA cũng cần có đồng hồ kỹ thuật số để điều khiển hoạt động của các Flip-Flop. Đồng hồ tạo ra các sóng vuông với cạnh lên, cạnh xuống, trạng thái cao, trạng thái thấp. Có thể hiểu mỗi tíck của đồng hồ kích thích hoạt động của Flip-Flop. Thường hay sử dụng thời điểm CẠNH LÊN.

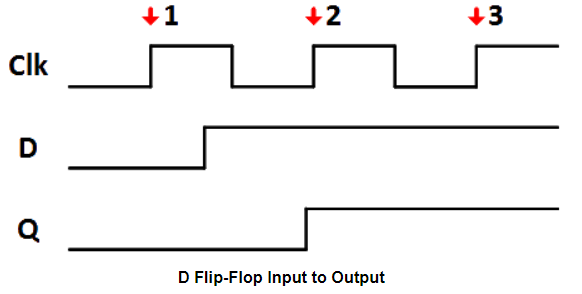

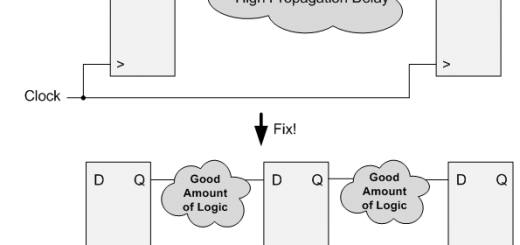

Đồng hồ cho phép sử dụng Flip-Flop như một phần tử lưu trữ dữ liệu. Bất kỳ phần tử lưu trữ dữ liệu nào được gọi là logic tuần tự hoặc logic đăng ký . Logic tuần tự hoạt động trên các chuyển tiếp của đồng hồ. 99,9% thời gian này sẽ là cạnh lên (khi đồng hồ đi từ 0 đến 1). Khi một Flip-Flop thấy một cạnh lên của đồng hồ, nó đăng ký dữ liệu từ đầu vào D ở đầu ra Q . Hãy xem xét một dạng sóng của một vài sự kiện.

Dạng sóng trên cho thấy ba sự kiện chu kỳ đồng hồ, được biểu thị bằng mũi tên màu đỏ trên cạnh lên của đồng hồ. Ở giữa cạnh tăng đầu tiên và thứ hai của đồng hồ, đầu vào D đi từ thấp đến cao. Đầu ra Q thấy rằng D đã đi từ thấp đến cao ở cạnh tăng của chu kỳ đồng hồ thứ hai. Cạnh tăng là khi Flip Flop nhìn vào dữ liệu đầu vào. Tại thời điểm này, Q trở thành giá trị giống như đầu vào D. Trên cạnh tăng thứ ba, Q lại kiểm tra giá trị của D và đăng ký nó (đây là lý do tại sao flip-flops thường được gọi là thanh ghi). Vì nó không thay đổi, Q vẫn ở mức cao. Hãy xem xét một dạng sóng khác.

Hình ảnh trên cho thấy một dạng sóng của hai đầu vào và một đầu ra cho một D Flip-Flop. D Flip-Flop nhạy cảm với cạnh tăng của đồng hồ, vì vậy khi cạnh tăng lên xuất hiện, đầu vào D được truyền đến đầu ra Q. Điều này chỉ xảy ra trên các cạnh . Trong chu kỳ đồng hồ đầu tiên, Q thấy rằng D đã trở thành 1, vì vậy nó chuyển đổi từ 0 đến 1. Trên cạnh đồng hồ thứ hai, Q lại kiểm tra giá trị của D và thấy rằng giá trị đó thấp một lần nữa, vì vậy nó trở nên thấp.

Bây giờ bạn đã hiểu cách chúng làm việc, hãy thảo luận tại sao chúng lại quan trọng trong thiết kế kỹ thuật số. Tôi xin nhắc lại rằng flip-flop và LUT là hai thành phần quan trọng nhất bên trong của một FPGA. Khái niệm về cách hoạt động của flip-flop (đăng ký) là rất quan trọng để trở thành một nhà thiết kế kỹ thuật số tốt. Flip-flops là thành phần chính trong một FPGA được sử dụng để giữ trạng thái bên trong của chip.

Nếu tất cả mọi thứ chỉ được thực hiện bởi LUT, sẽ không có cách nào để giữ trạng thái trong FPGA. Điều này có nghĩa là FPGA sẽ không có ý tưởng những gì đã xảy ra trước đó. Tất cả các thay đổi trên đầu vào sẽ ngay lập tức được đánh giá và gửi đến đầu ra với một chuỗi rất dài các cổng AND và cổng OR, vv Nhưng để làm đại đa số các nhiệm vụ mà FPGA cần biết một cái gì đó đã xẩy ra trong quá khứ. Bằng cách này, nó có thể theo dõi các bộ đếm, trạng thái máy và trạng thái của sự vật. Flip-flops giúp FPGA làm được điều này. Nếu bạn vẫn chưa nắm bắt được khái niệm này, thì không sao. Vì sau này bạn sẽ được tiếp xúc rất nhiều đến Flip-Flop. Tầm quan trọng của flip-flops trong thiết kế FPGA của bạn sẽ trở nên rõ ràng hơn bạn càng làm việc với một ngôn ngữ mô tả phần cứng (HDL) được đề cập trong những phần sau.

Bình luận gần đây