Bài 12: Thời gian thiết lập và thời gian giữ tín hiệu trong FPGA.

Thời gian thiết lập và thời gian giữ tín hiệu trong FPGA là gì?

Thời gian thiết lập và thời gian giữ là các khái niệm quan trọng cần hiểu cho mọi nhà thiết kế kỹ thuật số. Bài viết này giải thích về thời gian thiết lập và thời gian giữ tín hiệu và cách chúng được sử dụng bên trong của một FPGA.

Bài viết này giả định rằng người đọc có hiểu biết cơ bản về Flip-Flop là gì và sự chậm trễ lan truyền ảnh hưởng đến thiết kế như thế nào (xem các bài trước).

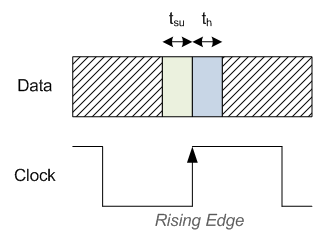

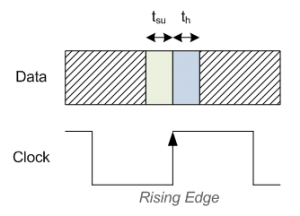

Nhắc lại một chút, sự chậm trễ lan truyền là khoảng thời gian cần thiết cho các tín hiệu truyền giữa hai Flip-Flops. Khi tín hiệu truyền xuống một dây, nó có thể thay đổi từ 0 sang 1 hoặc 1 sang 0. Đầu vào cho Flip-Flop cần phải được ổn định (không thay đổi) để cho một thiết kế FPGA hoạt động đúng. Đầu vào phải ổn định trong một khoảng thời gian nhỏ trước khi được lấy mẫu bởi đồng hồ. Lượng thời gian này được gọi là thời gian thiết lập . Thời gian thiết lập là khoảng thời gian cần thiết cho đầu vào cho Flip-Flop để ổn định trước một cạnh đồng hồ . Thời gian giữ tương tự với thời gian thiết lập, nhưng nó đề cập đến các sự kiện sau khi một cạnh đồng hồ xảy ra. Thời gian giữ là khoảng thời gian tối thiểu cần thiết để đầu vào cho Flip-Flop ổn định sau một cạnh đồng hồ.

Trong hình, vùng màu xanh lá đại diện cho t su là thời gian thiết lập (SetupTime). Vùng màu xanh dương đại diện cho t h hoặc Thời gian giữ (hold). Trong các khu vực này, dữ liệu vào Flip-Flop có thể là 0 hoặc 1 hoặc lơ lững (không rõ ràng 0 hay 1).

Thời gian thiết lập và thời gian giữ liên quan gì đến sự chậm trễ truyền và tần số đồng hồ?

Thời gian thiết lập, thời gian giữ và sự chậm trễ lan truyền đều ảnh hưởng đến thiết kế thời gian trong FPGA của bạn. Các công cụ FPGA sẽ kiểm tra để đảm bảo rằng thiết kế của bạn đáp ứng thời gian, có nghĩa là đồng hồ không chạy nhanh hơn logic cho phép. Lượng thời gian tối thiểu được phép cho đồng hồ FPGA của bạn (Thời gian của nó, được biểu diễn bằng T ) có thể được tính toán. Từ đó bạn có thể tìm thấy tần số của đồng hồ, vì tần số là nghịch đảo của chu kỳ ( F = 1 / T ). Nó là như sau:

t clk (min) = t su + t h + t p

Nói chung trong thiết kế FPGA của bạn, t su và t h được cố định cho Flip-Flops của bạn, do đó, biến duy nhất mà bạn có quyền kiểm soát là t p hoặc sự chậm trễ truyền. Độ trễ này thể hiện số lượng nội dung bạn đang cố thực hiện trong một chu kỳ đồng hồ. Càng nhiều thứ bạn cố gắng làm, tp càng dài và tclk(min) càng lớn, nghĩa là bạn sẽ không thể thiết kế FPGA chạy nhanh hơn tclk(min) này. Được cái nọ thì mất cái kia nhé!

Nếu thiết kế của bạn vi phạm thời gian thiết lập hoặc thời gian giữ, đầu ra Flip-Flop không được đảm bảo ổn định. Nó có thể bằng không, nó có thể là một, nó có thể ở đâu đó ở giữa, nó không biết được. Điều này được gọi là metastability. Metastability bên trong FPGA là điều không mong muốn, nó có thể làm cho FPGA của bạn cư xử kỳ lạ. Vật lý đằng sau tính metastability rất thú vị, bạn có thể đọc thêm về metastability ở đây.

Cách chính mà một nhà thiết kế FPGA phát hiện ra nếu họ đã vi phạm thòi gian thiết lập hoặc thời giữ là khi chạy FPGA thông qua Place và Route . Place và Route là những gì sẽ xảy ra khi bạn lấy mã VHDL hoặc Verilog của bạn và đặt nó vào một FPGA. Là một phần của quá trình này, các công cụ FPGA sẽ lấy thiết kế của bạn và chạy một phân tích thời gian. Chính trong phân tích thời gian này, bạn sẽ thấy bất kỳ lỗi thời gian nào, thực sự chỉ là vi phạm thời gian thiết lập hoặc thời gian giữ. Cách khắc phục các lỗi này nằm ngoài phạm vi của bài viết này, nhưng hãy đọc bài viết về sự chậm trễ truyền để xem các lỗi thời gian này có thể được sửa như thế nào.

Câu hỏi

-

- Q. Nếu Flip-Flop có thời gian thiết lập 1 nano giây (ns), thời gian tối thiểu cần thiết để dữ liệu ổn định trước đồng hồ là bao nhiêu?

- A. 1 ns. Đây là định nghĩa về thời gian thiết lập

-

- Q. Nếu hai Flip-Flops có thời gian thiết lập 1 ns, thời gian giữ 1 ns và 8 ns trễ truyền, tần số tối đa mà đồng hồ này có thể chạy là bao nhiêu?

- A. t clk (min) = t su + t h + t p . Vì vậy, t clk (min) = 1 ns + 1 ns + 8 ns = 10 ns. Với F = 1 / T, trong đó T = 10 ns. F = 100 MHz.

-

- Q. Nếu bạn có đồng hồ 50 MHz, thời gian thiết lập 1 ns và thời gian giữ 2 ns, thiết kế của bạn sẽ cho phép độ trễ truyền tối đa giữa hai flip-flops là gì?

- A. t clk (min) = t su + t h + t p . Vì F = 1 / T, t clk = 20 ns. Vì vậy, 20 ns = 1 ns + 2 ns + t p . Vậy: t p = 17 ns.

- Q. Nếu bạn có một đồng hồ 200 MHz và bạn có lỗi thời gian sau khi chạy qua Place và Route, bạn có thể làm gì để sửa lỗi này?

- A. Các lỗi thời gian được gây ra khi bạn vi phạm phương trình t clk (min) = t su + t h + t p .Khi thời gian thiết lập thời gian, thời gian giữ, và tần số đồng hồ được cố định, biến duy nhất bạn có thể can thiệp là thời gian truyền t p . Cách đơn giản nhất để giảm thời gian truyền là giảm số lượng nội dung mà bạn đang cố gắng hoàn thành trong 1 chu kỳ đồng hồ. Chia logic của bạn từ 1 chu kỳ đồng hồ thành 2 chu kỳ đồng hồ trở lên. Để biết thêm thông tin về điều này, hãy đọc bài viết về sự chậm trễ lan truyền .

Bài viết của bạn thật tốt, mình đọc cảm thấy rất dễ hiểu và giải đáp cho mình một số kiến thức mà trước đây hơi ” lơ mơ” về FPGA.